-

Mail us

sale@tiger-transformer.com -

Phone us

(+86)15155183777

Mail us

sale@tiger-transformer.comPhone us

(+86)1515518377701

The Global Challenge of Chip EDA

The important value and contribution of the development of the industry is beyond doubt. With the continuous advancement of "Beyond Moore" and "Deep Moore" in the post-Moore era, chip design is facing new challenges. As pointed out by Synopsys, the most complex chip designs today contain more than 1.2 trillion transistors and 400,000 AI-optimized cores, making it largely difficult for human designers to meet the requirements of commercial efficiency.

Therefore, it is necessary to use AI to achieve faster, more efficient, and lowest overall cost chip design. In fact, amazing breakthroughs have been made in AI-enabled EDA design. Taking Aera (area) in PPAC as a breakthrough, using AI-based Design Space Optimization (DSO) technology to replace traditional Design Space Exploration (DSE) has become the best solution for automatic design space search One of the options. MediaTek showed that it used AI tools to reduce the size of a key processor component by 5 percent and reduce power consumption by 6 percent. Cadence used AI to help an engineer improve the performance of a 5nm mobile chip by 14% and reduce its power consumption by 3% in 10 days, which previously required 10 engineers to complete for several months.

02

RF Chip: The Crown Jewel

RF technology is used to transmit and Technology for receiving high-frequency radio wave energy, and radio frequency chips are electronic chips used to receive and transmit radio frequency radio signals. RF chips are the cornerstone of all modern wireless communications and are known as the jewel in the crown of analog chips. The 5G technology that entered the market in 2019 has opened the ceiling of the radio frequency industry. According to the research data of QYR Electronic Research Center, the market size of the global radio frequency front-end alone will reach 31.3 billion US dollars in 2023, with a compound annual growth rate of more than 15%. From a specific example, the number of radio frequency devices and circuits in a 5G smartphone is more than twice that of a 4G mobile phone, and the value is also more than 2-5 times that of a 4G mobile phone, and it is more than 10 times that of a 3G mobile phone. In the future, the development of 5G/6G communication, the application of Satellite Internet (Starlink), and the realization of Intelligent Connection of Everything will further greatly promote the radio frequency The demand and growth of technology, especially radio frequency chips.

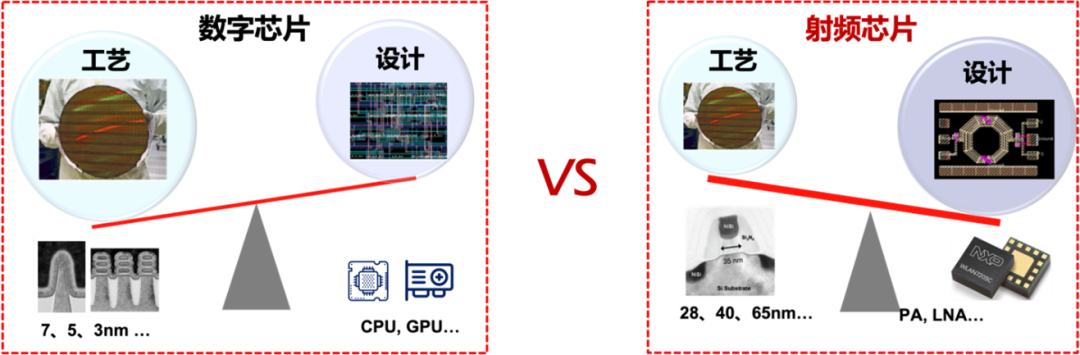

Unlike digital chips (CPU, GPU, etc.) which rely heavily on advanced semiconductor manufacturing technology, RF chip design is extremely difficult and often requires IC engineers to "carve out". RF chip design contains not only active circuits, but also a large number of passive parts such as inductors, transformers and matching networks. Among them, passive components and circuits usually need to be iterated repeatedly by electromagnetic simulation combined with the layout, which has become a key difficulty in RF design.

03

AI-enabled RF design tools

Ran Puwei is the pioneer of chip intelligent design tools in the post-EDA era, focusing on Use AI technology to design complex and diverse RF chips. The founding team of scientists, based on decades of rich experience in the world's top chip design companies, combined with the world's leading AI technology advantages, aimed at the difficulties of RF chip design, launched the "computationally generated" RF integrated circuit intelligent generation artifact "IC-Prophet" .

"IC-Prophet" can directly calculate the optimal design parameters through AI algorithm according to the design indicators (such as inductance value, Q value, gain, etc.) that the designer needs to achieve, and use AI technology Generate design-rule-compliant GDSII layouts for direct use by RF circuit design developers in any industry-standard design tool such as Cadence Virtuoso. "IC-Prophet" fundamentally changes the traditional design process from the design methodology, saves design engineers from the hard work of repeated simulation iterations, and helps RF design engineers greatly improve the efficiency and capability of RF chip design. Take the design of inductors commonly used in RF circuits as an example:

After a year of pre-tool testing and tape-out verification, Ran Puwei's “IC-Prophet” V1.625 version Has been officially updated and launched, currently covering 22nm, 28nm, 40nm, 55nm, 65nm > and 130nm and other commonly used CMOS process nodes for RF design, as well as passive components and circuits commonly used for RF design such as inductors, transformers, matching networks.